# **LARA-R2** series

# Size-optimized LTE Cat 1 modules in single and multimode configurations

**Data sheet**

### **Abstract**

Technical data sheet describing the LARA-R2 series multi-mode cellular modules. The modules are a cost efficient and performance optimized LTE Cat 1 / 3G / 2G multi-mode solution covering up to four LTE bands, up to two UMTS/HSPA bands and up to two GSM/EGPRS bands in the very small and compact LARA form factor.

# **Document information**

| Title                  | LARA-R2 series                                                     |             |  |  |  |  |  |

|------------------------|--------------------------------------------------------------------|-------------|--|--|--|--|--|

| Subtitle               | Size-optimized LTE Cat 1 modules in single and multi-mode configur |             |  |  |  |  |  |

| Document type          | Data sheet                                                         |             |  |  |  |  |  |

| Document number        | UBX-16005783                                                       |             |  |  |  |  |  |

| Revision and date      | R28                                                                | 23-Jun-2021 |  |  |  |  |  |

| Disclosure restriction | C1-Public                                                          |             |  |  |  |  |  |

| Product status                   | Corresponding content status |                                                                                        |  |  |  |  |  |  |

|----------------------------------|------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Functional sample                | Draft                        | For functional testing. Revised and supplementary data will be published later.        |  |  |  |  |  |  |

| In development /<br>Prototype    | Objective specification      | Target values. Revised and supplementary data will be published later.                 |  |  |  |  |  |  |

| Engineering sample               | Advance information          | Data based on early testing. Revised and supplementary data will be published later.   |  |  |  |  |  |  |

| Initial production               | Early production information | Data from product verification. Revised and supplementary data may be published later. |  |  |  |  |  |  |

| Mass production /<br>End of life | Production information       | Document contains the final product specification.                                     |  |  |  |  |  |  |

This document applies to the following products:

| Product name | Type number      | Modem version | Application version | PCN reference | Product status  |

|--------------|------------------|---------------|---------------------|---------------|-----------------|

| LARA-R202    | LARA-R202-02B-00 | 30.42         | A01.00              | UBX-17057959  | Obsolete        |

|              | LARA-R202-02B-01 | 30.42         | A01.01              | UBX-18018067  | Obsolete        |

|              | LARA-R202-02B-02 | 30.42         | A01.02              | UBX-18057549  | Obsolete        |

|              | LARA-R202-02B-03 | 30.44         | A01.02              | UBX-19011731  | End of life     |

|              | LARA-R202-02B-04 | 30.44         | A01.02              | UBX-21008753  | Mass production |

|              | LARA-R202-82B-00 | 30.53         | A01.03              | UBX-19043497  | End of life     |

|              | LARA-R202-82B-01 | 30.53         | A01.03              | UBX-21008753  | Mass production |

|              | LARA-R202-03B-00 | 30.55         | A01.00              | UBX-20027523  | Mass production |

| LARA-R203    | LARA-R203-02B-00 | 30.39         | A01.00              | UBX-17048311  | Obsolete        |

|              | LARA-R203-02B-01 | 30.39         | A01.02              | UBX-18018067  | Obsolete        |

|              | LARA-R203-02B-02 | 30.39         | A01.03              | UBX-18057549  | Obsolete        |

|              | LARA-R203-02B-03 | 30.41         | A01.03              | UBX-19011731  | End of life     |

|              | LARA-R203-02B-04 | 30.41         | A01.03              | UBX-21013811  | Mass production |

|              | LARA-R203-02B-34 | 30.54         | A01.00              | UBX-19056532  | End of life     |

|              | LARA-R203-02B-35 | 30.54         | A01.00              | UBX-21013810  | Mass production |

|              | LARA-R203-03B-00 | 30.55         | A01.00              | UBX-20027523  | Mass production |

| _ARA-R204    | LARA-R204-02B-00 | 31.34         | A01.00              | UBX-17012269  | Obsolete        |

|              | LARA-R204-02B-02 | 31.40         | A01.00              | UBX-18046834  | Mass production |

| _ARA-R211    | LARA-R211-02B-00 | 30.31         | A01.00              | UBX-17012270  | Obsolete        |

|              | LARA-R211-02B-01 | 30.49         | A01.01              | UBX-17054295  | Obsolete        |

|              | LARA-R211-02B-02 | 30.49         | A01.02              | UBX-18057549  | End of life     |

|              | LARA-R211-02B-03 | 30.49         | A01.05              | UBX-20012865  | End of life     |

|              | LARA-R211-02B-04 | 30.49         | A01.05              | UBX-21013808  | Mass production |

| LARA-R220    | LARA-R220-62B-00 | 30.44         | A01.03              | UBX-17061668  | Obsolete        |

|              | LARA-R220-62B-01 | 30.44         | A01.04              | UBX-18050698  | Obsolete        |

|              | LARA-R220-62B-02 | 30.44         | A01.05              | UBX-18057549  | Obsolete        |

|              | LARA-R220-62B-03 | 30.44         | A01.07              | UBX-19029271  | Mass production |

| LARA-R280    | LARA-R280-02B-00 | 30.43         | A01.01              | UBX-17063950  | Obsolete        |

|              | LARA-R280-02B-01 | 30.43         | A01.02              | UBX-18018067  | Obsolete        |

|              | LARA-R280-02B-02 | 30.43         | A01.03              | UBX-18052020  | Obsolete        |

|              | LARA-R280-02B-03 | 30.43         | A01.04              | UBX-18057549  | End of life     |

|              | LARA-R280-02B-04 | 30.43         | A01.06              | UBX-19029271  | Mass production |

| LARA-R281    | LARA-R281-02B-00 | 30.49         | A01.06              | UBX-20035136  | Mass production |

u-blox or third parties may hold intellectual property rights in the products, names, logos and designs included in this document. Copying, reproduction, modification or disclosure to third parties of this document or any part thereof is only permitted with the express written permission of u-blox.

The information contained herein is provided "as is" and u-blox assumes no liability for its use. No warranty, either express or implied, is given, including but not limited to, with respect to the accuracy, correctness, reliability and fitness for a particular purpose of the information. This document may be revised by u-blox at any time without notice. For the most recent documents, visit www.u-blox.com.

Copyright © u-blox AG.

# **Contents**

| Document information                                   | 2  |

|--------------------------------------------------------|----|

| Contents                                               | 4  |

| 1 Functional description                               | 6  |

| 1.1 Overview                                           | 6  |

| 1.2 Product features                                   | 7  |

| 1.3 Block diagram                                      | 8  |

| 1.4 Product description                                | 8  |

| 1.5 AT command support                                 | 10 |

| 1.6 Supported features                                 | 10 |

| 2 Interfaces                                           | 12 |

| 2.1 Power management                                   | 12 |

| 2.1.1 Module supply input (VCC)                        |    |

| 2.1.2 RTC supply input / output (V_BCKP)               |    |

| 2.1.3 Generic digital interfaces supply output (V_INT) |    |

| 2.2 Antenna interfaces                                 | 12 |

| 2.2.1 Antenna RF interfaces                            | 12 |

| 2.2.2 Antenna detection                                |    |

| 2.3 System functions                                   |    |

| 2.3.1 Module power-on                                  |    |

| 2.3.2 Module power-off                                 |    |

| 2.3.3 Module reset                                     |    |

| 2.3.4 Module / host configuration selection            |    |

| 2.4 SIM                                                |    |

| 2.4.1 SIM interface                                    |    |

| 2.4.2 SIM detection                                    |    |

| 2.5 Serial communication                               |    |

| 2.5.1 Main UART interface                              |    |

| 2.5.2 Auxiliary UART interface                         |    |

| 2.5.3 USB interface                                    |    |

| 2.5.4 HSIC interface                                   |    |

| 2.5.5 DDC (I2C) interface                              |    |

| 2.5.6 SDIO interface                                   |    |

| 2.6 Audio                                              |    |

| 2.7 Clock output                                       |    |

| 2.8 GPIO                                               |    |

| 3 Pin definition                                       |    |

| 3.1 Pin assignment                                     |    |

| 4 Electrical specifications                            |    |

| 4.1 Absolute maximum rating                            |    |

| 4.1.1 Maximum ESD                                      |    |

| 4.2 Operating conditions                               | 26 |

|   | 4.2.1         | Operating temperature range     | 26  |

|---|---------------|---------------------------------|-----|

|   | 4.2.2         | Supply/power pins               | .26 |

|   | 4.2.3         | Current consumption             | .27 |

|   | 4.2.4         | LTE RF characteristics          | .28 |

|   | 4.2.5         | 3G RF characteristics           | .30 |

|   | 4.2.6         | 2G RF characteristics           | .30 |

|   | 4.2.7         | ANT_DET pin                     | .31 |

|   | 4.2.8         | PWR_ON pin                      | 31  |

|   | 4.2.9         | RESET_N pin                     | .31 |

|   | 4.2.10        | SIM pins                        | .31 |

|   | 4.2.11        | USB pins                        | .32 |

|   | 4.2.12        | PHSIC pins                      | .32 |

|   |               | B DDC (I2C) pins                |     |

|   | 4.2.14        | Generic Digital Interfaces pins | 33  |

|   | 4.3 Par       | ameters for ATEX applications   | .35 |

| 5 | Mech          | anical specifications           | 36  |

| 6 | Quali         | fication and approvals          | 37  |

|   | 6.1 Rel       | iability tests                  | .37 |

|   | 6.2 App       | orovals                         | .37 |

| 7 | ' Produ       | uct handling & soldering        | 38  |

|   | 7.1 Pag       | kaging                          | .38 |

|   | 7.1.1         | Reels                           | .38 |

|   | 7.1.2         | Tapes                           | 39  |

|   | 7.2 Mo        | isture sensitivity levels       | .40 |

|   | 7.3 Ref       | low soldering                   | .40 |

|   | 7.4 ESI       | O precautions                   | .40 |

| 8 | Defa          | ılt settings                    | 41  |

| 9 | Labe          | ling and ordering information   | 42  |

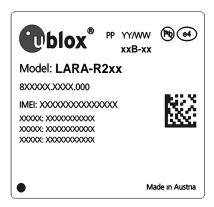

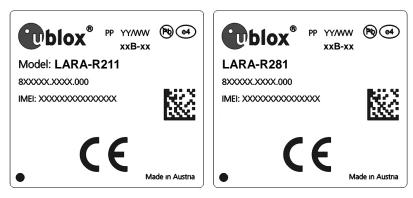

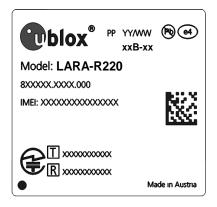

|   | 9.1 Pro       | duct labeling                   | .42 |

|   | 9.2 Exp       | planation of codes              | .43 |

|   | 9.3 Ord       | lering information              | .44 |

| Δ | ppendix       | C                               | 45  |

| Δ | Gloss         | eary                            | 45  |

| F | Related o     | documentation                   | 46  |

|   |               | history                         |     |

|   |               |                                 |     |

| • | , <del></del> |                                 |     |

# 1 Functional description

## 1.1 Overview

The LARA-R2 series comprises LTE Cat 1/3G/2G multi-mode modules in the very small LARA LGA form-factor (26.0 x 24.0 mm, 100-pin) that are easy to integrate in compact designs.

LARA-R2 series modules support multi-band LTE-FDD Cat 1 radio access technology with seven regional variants. Each variant is designed for specific regional market requirements to allow development of cost efficient yet feature-rich products. The variants with 2G or 3G fallback provide connectivity in cases where LTE coverage is not yet available. This allows seamless operation during technology transition.

LARA modules are form-factor compatible with u-blox SARA, LISA and TOBY cellular module families: this facilitates easy migration from u-blox GSM/GPRS, CDMA, UMTS/HSPA, and other LTE modules, maximizes the investments of customers, simplifies logistics, and enables very short time-to-market.

The modules are ideal for applications that are transitioning to LTE from 2G and 3G, due to the long term availability and scalability of LTE networks.

With a range of interface options and an integrated IP stack, the modules are designed to support a wide range of data-centric applications. The unique combination of performance and flexibility make these modules ideally suited for medium speed M2M applications, such as smart energy gateways, remote access video cameras, digital signage, telehealth and telematics.

LARA-R2 series modules include product versions supporting Voice over LTE (VoLTE) and voice over 3G or 2G (CSFB) for applications that require voice, such as security and surveillance systems.

Thanks to the u-blox's CellLocate® technology, LARA-R2 series modules offer cost-effective location estimation based on information from surrounding cellular base stations. A positioning solution with CellLocate® and a u-blox GNSS module provides redundancy and accuracy that can be beneficial for numerous applications.

The temperature range of -40 °C to +85 °C guarantees operation in harsh environments and in very compact designs.

LARA-R2 modules are manufactured in ISO/TS 16949 certified sites, with the highest production standards and the highest quality and reliability. Each module is fully tested and inspected during production. Modules are qualified according to ISO 16750 – for systems installed in vehicles.

USB drivers and RIL software for Android are free of charge.

## 1.2 Product features

| Model     | Region           | Radio access<br>technology |             | Pos         |                |                    | Positioning |                       |         | Interfaces |        |                    | Au    | dio          | Features      |                    |       |                    | Grade                  |                       | е                    |             |              |                        |          |              |            |

|-----------|------------------|----------------------------|-------------|-------------|----------------|--------------------|-------------|-----------------------|---------|------------|--------|--------------------|-------|--------------|---------------|--------------------|-------|--------------------|------------------------|-----------------------|----------------------|-------------|--------------|------------------------|----------|--------------|------------|

|           |                  | LTE bands¹                 | UMTS bands  | GSM bands   | GNSS via modem | AssistNow Software | CellLocate® | UART                  | USB 2.0 | HISC *     | * OIOS | DDC (1 <u>2</u> C) | GPIOs | Analog audio | Digital audio | Network indication | VoLTE | Antenna supervisor | Embedded TCP/UDP stack | Embedded HTTP,FTP,TSL | FW update via serial | FOTA client | Rx Diversity | Dual stack IPv4 / IPv6 | Standard | Professional | Automotive |

| LARA-R202 | North<br>America | 2,4<br>5,12                | 850<br>1900 | )           | •              | •                  | •           | <b>2</b> <sup>2</sup> | 1       | 1          | 1      | 1                  | 9     |              | •             | •                  | •3    | •                  | •                      | •                     | •                    | •           | •            | •                      |          | •            |            |

| LARA-R203 | North<br>America | 2,4,12                     |             |             | •              | •                  | •           | <b>2</b> <sup>2</sup> | 1       | 1          | 1      | 1                  | 9     |              | •             | •                  | •3    | •                  | •                      | •                     | •                    | •           | •            | •                      |          | •            |            |

| LARA-R204 | North<br>America | 4,13                       |             |             |                |                    |             | 1                     | 1       | 1          | 1      | 1                  | 9     |              |               | •                  |       | •                  | •                      | •                     | •                    | •           | •            | •                      |          | •            |            |

| LARA-R211 | EMEA             | 3,7,20                     |             | 900<br>1800 | •4             | •4                 | •4          | 2 <sup>5</sup>        | 1       | 1          | 1      | 1                  | 9     |              | •             | •                  | •     | •                  | •                      | •                     | •                    | •           | •            | •                      |          | •            |            |

| LARA-R220 | Japan            | 1,19                       |             |             | •              | •                  | •           | 1                     | 1       | 1          | 1      | 1                  | 9     |              |               | •                  |       | •                  | •                      | •                     | •                    | •           | •            | •                      |          | •            |            |

| LARA-R280 | APAC             | 3,8,28                     | 2100        | )           | •              | •                  | •           | 1                     | 1       | 1          | 1      | 1                  | 9     |              | •             | •                  | •     | •                  | •                      | •                     | •                    | •           | •            | •                      |          | •            |            |

| LARA-R281 | EMEA             | 1,3,8<br>20,28             | 2100        | ١           | •              | •                  | •           | 1                     | 1       | 1          | 1      | 1                  | 9     |              | •             | •                  | •     | •                  | •                      | •                     | •                    | •           | •            | •                      |          | •            |            |

<sup>• =</sup> Available in any firmware

■ = CSFB only

\* = HW ready

Table 1: LARA-R2 series main features summary

<sup>&</sup>lt;sup>1</sup> LTE band 12 is a superset including band 17: LTE band 12 is supported along with Multi-Frequency Band Indicator (MFBI)

<sup>&</sup>lt;sup>2</sup> Second UART not supported by LARA-R202-02B, LARA-R202-82B, or LARA-R203-02B product versions

$<sup>^{\</sup>rm 3}$  AT&T certified with VoLTE

<sup>&</sup>lt;sup>4</sup> External GNSS control via modem, AssistNow Software and CellLocate® are not supported by LARA-R211-02B-00

<sup>&</sup>lt;sup>5</sup> Second UART is not supported by LARA-R211-02B-00, LARA-R211-02B-01, or LARA-R211-02B-02 product versions

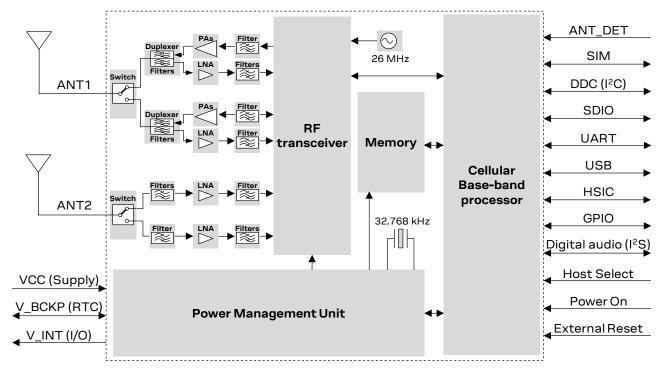

## 1.3 Block diagram

Figure 1: LARA-R2 series block diagram

The "02B", "62B", "82B", and "03B" product versions of u-blox LARA-R2 series modules (meaning the LARA-R202-02B, LARA-R202-82B, LARA-R202-03B, the LARA-R203-02B, LARA-R203-03B, the LARA-R204-02B, the LARA-R211-02B, the LARA-R220-62B, the LARA-R280-02B, and the LARA-R281-02B) do not support the following interfaces, which can be left unconnected and should not be driven by external devices:

- o HSIC interface

- o SDIO interface

- HOST\_SELECT pin

## 1.4 Product description

LARA-R2 series modules provide LTE Cat 1 radio access technology, some variants with 2G or 3G multi-mode fallback.

- LARA-R202 is designed mainly for operation in America (on LTE and 3G networks)

- LARA-R203 is designed mainly for operation in America (on LTE networks)

- LARA-R204 is designed mainly for operation in America (on Verizon LTE network)

- LARA-R211 is designed mainly for operation in EMEA on LTE and 2G networks

- LARA-R220 is designed mainly for operation in Japan (on NTT DoCoMo LTE network)

- LARA-R280 is designed mainly for operation in APAC on LTE and 3G networks

- LARA-R281 is designed mainly for operation in EMEA on LTE and 3G networks

| 4G LTE                                                                                                                                                               | 3G UMTS/HSDPA/HSUPA                                                                                                                  | 2G GSM/GPRS/EDGE                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3GPP Release 9<br>Long Term Evolution (LTE)                                                                                                                          | 3GPP Release 9 High Speed Packet Access (HSPA)                                                                                       | 3GPP Release 9 Enhanced Data rate GSM Evolution (EDGE)                                                                                                                                                                                           |

| Evolved UTRA (E-UTRA) Frequency Division Duplex (FDD) DL Rx diversity                                                                                                | UMTS Terrestrial Radio Access (UTRA) Frequency Division Duplex (FDD) DL Rx Diversity                                                 | GSM EGPRS Radio Access (GERA) Time Division Multiple Access (TDMA) DL Advanced Rx Performance Phase 1                                                                                                                                            |

| Band support <sup>6</sup> :  LARA-R202: Band 12 (700 MHz) <sup>7</sup> Band 5 (850 MHz) Band 4 (1700 MHz) Band 2 (1900 MHz)                                          | Band support:  LARA-R202: Band 5 (850 MHz) Band 2 (1900 MHz)                                                                         | Band support:                                                                                                                                                                                                                                    |

| <ul> <li>LARA-R203:</li> <li>Band 12 (700 MHz)<sup>7</sup></li> <li>Band 4 (1700 MHz)</li> <li>Band 2 (1900 MHz)</li> <li>LARA-R204:</li> </ul>                      |                                                                                                                                      |                                                                                                                                                                                                                                                  |

| <ul><li>Band 13 (700 MHz)</li><li>Band 4 (1700 MHz)</li></ul>                                                                                                        |                                                                                                                                      |                                                                                                                                                                                                                                                  |

| <ul> <li>LARA-R211:</li> <li>Band 20 (800 MHz)</li> <li>Band 3 (1800 MHz)</li> <li>Band 7 (2600 MHz)</li> </ul>                                                      |                                                                                                                                      | <ul><li>LARA-R211:</li><li>E-GSM 900 MHz</li><li>DCS 1800 MHz</li></ul>                                                                                                                                                                          |

| <ul><li>LARA-R220:</li><li>Band 19 (850 MHz)</li><li>Band 1 (2100 MHz)</li></ul>                                                                                     |                                                                                                                                      |                                                                                                                                                                                                                                                  |

| <ul><li>LARA-R280:</li><li>Band 28 (700 MHz)</li><li>Band 8 (900 MHz)</li><li>Band 3 (1800 MHz)</li></ul>                                                            | <ul><li>LARA-R280:</li><li>Band 1 (2100 MHz)</li></ul>                                                                               |                                                                                                                                                                                                                                                  |

| <ul> <li>LARA-R281:</li> <li>Band 28 (700 MHz)</li> <li>Band 20 (800 MHz)</li> <li>Band 8 (900 MHz)</li> <li>Band 3 (1800 MHz)</li> <li>Band 1 (2100 MHz)</li> </ul> | <ul><li>LARA-R281:</li><li>Band 1 (2100 MHz)</li></ul>                                                                               |                                                                                                                                                                                                                                                  |

| LTE Power Class • Power Class 3 (23 dBm)                                                                                                                             | UMTS/HSDPA/HSUPA Power Class • Class 3 (24 dBm)                                                                                      | GSM/GPRS (GMSK) Power Class  • Power Class 4 (33 dBm) for E-GSM band  • Power Class 1 (30 dBm) for DCS band                                                                                                                                      |

|                                                                                                                                                                      |                                                                                                                                      | <ul> <li>EDGE (8-PSK) Power Class</li> <li>Power Class E2 (27 dBm) for E-GSM band</li> <li>Power Class E2 (26 dBm) for DCS band</li> </ul>                                                                                                       |

| Data rate  LTE category 1: up to 10.3 Mbit/s DL, up to 5.2 Mbit/s UL                                                                                                 | <ul> <li>Data rate</li> <li>HSDPA category 8:<br/>up to 7.2 Mbit/s DL</li> <li>HSUPA category 6:<br/>up to 5.76 Mbit/s UL</li> </ul> | <ul> <li>Data rate<sup>8</sup></li> <li>GPRS multi-slot class 33<sup>9</sup>, CS1-CS4, up to 107 kbit/s DL, up to 85.6 kbit/s UL</li> <li>EDGE multi-slot class 33<sup>9</sup>, MCS1-MCS9, up to 296 kbit/s DL, up to 236.8 kbit/s UL</li> </ul> |

LARA-R2 modules provide Voice over LTE (VoLTE)<sup>10</sup> as well as Circuit-Switched-Fall-Back (CSFB)<sup>11</sup> audio capability.

UBX-16005783 - R28 C1-Public

<sup>&</sup>lt;sup>6</sup> LARA-R2 modules support all E-UTRA channel bandwidths for each operating band according to 3GPP TS 36.521-1 [11]

<sup>&</sup>lt;sup>7</sup> LTE band 12 is a superset including band 17: LTE band 12 is supported along with Multi-Frequency Band Indicator feature

<sup>&</sup>lt;sup>8</sup> GPRS/EDGE multislot class determines the number of timeslots available for upload and download and thus the speed at which data can be transmitted and received, with higher classes typically allowing faster data transfer rates.

$<sup>^9</sup>$  GPRS/EDGE multislot class 33 implies a maximum of 5 slots in DL (reception), 4 slots in UL (transmission) with 6 slots in total.

<sup>&</sup>lt;sup>10</sup> Not supported by LARA-R204-02B, LARA-R220-62B, LARA-R280-02B and LARA-R281-02B modules product versions.

<sup>&</sup>lt;sup>11</sup> Not supported by LARA-R203-02B, LARA-R203-03B, LARA-R204-02B and LARA-R220-62B modules product versions.

## 1.5 AT command support

The LARA-R2 series modules support AT commands according to 3GPP standards TS 27.007 [7], TS 27.005 [8] and the u-blox AT command extension.

**T**

For the complete list of all supported AT commands and their syntax, see the u-blox AT commands manual [1].

RIL (Radio Interface Layer) software for Android and Embedded Windows is available for LARA-R2 series modules free of charge; see the Android RIL source code application note [3] for the supported software deliveries and more information.

## 1.6 Supported features

Table 3 lists some of the main features supported by LARA-R2 series. For more details, see LARA-R2 series system integration manual [2] and u-blox AT commands manual [1].

| Feature                                                     | Description                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Network indication                                          | GPIO configured to indicate the network status: registered home network, registered roaming, voice or data call enabled, no service. The feature can be enabled through the +UGPIOC AT command.                                                                                                                                |

| Antenna detection                                           | The ANT_DET pin provides antenna presence detection capability, evaluating the resistance from ANT1 and ANT2 pins to GND by means of an external antenna detection circuit implemented on the application board.  The antenna detection feature can be enabled through the +UANTR AT command.                                  |

| Embedded TCP and<br>UDP stack                               | Embedded TCP/IP and UDP/IP stack including direct link mode for TCP and UDP sockets.  Sockets can be set in Direct Link mode to establish a transparent end to end communication with an already connected TCP or UDP socket via serial interface.                                                                             |

| FTP, FTPS                                                   | File Transfer Protocol as well as Secure File Transfer Protocol (SSL encryption of FTP control channel) functionalities are supported by means of AT commands.                                                                                                                                                                 |

| HTTP, HTTPS                                                 | Hyper-Text Transfer Protocol and Secure Hyper-Text Transfer Protocol (SSL encryption) functions are supported via AT commands. HEAD, GET, POST, DELETE and PUT operations are available.                                                                                                                                       |

| Embedded TLS 1.2                                            | With the support of X.509 certificates, Embedded TLS 1.2 provides server and client authentication, data encryption, data signature and enables TCP/IP applications like HTTPS and FTPS to communicate over a secured and trusted connection.  The feature can be configured and enabled by +USECMNG and +USECPRF AT commands. |

| DNS                                                         | Support for DNS functionality.                                                                                                                                                                                                                                                                                                 |

| IPv4/lpv6 dual-stack                                        | Can move between Ipv4 and dual stack network infrastructures. Ipv4 and Ipv6 addresses can be used.                                                                                                                                                                                                                             |

| PPP                                                         | lpv4/lpv6 packets relaying through the cellular protocol stack performed on a Point-to-Point Protocol connection established with the external application via a serial interface (UART, MUX, or CDC-ACM). Transitions between Online command mode (OLCM) and PPP mode are supported.                                          |

| BIP                                                         | Bearer Independent Protocol for Over-the-Air SIM provisioning. The data transfer to/from the SIM uses either an already active PDP context or a new PDP context established with the APN provided by the SIM card.                                                                                                             |

| Multiple PDP contexts                                       | Up to 8 PDP contexts can be activated, and multi secondary PDP contexts be associated to a primary PDP context.                                                                                                                                                                                                                |

| VoLTE <sup>12</sup> and CSFB <sup>13</sup> audio capability | Voice over LTE (VoLTE) feature allows voice service over LTE bearer, via embedded IP Multimedia Subsystem (IMS).  Circuit Switched Fall-Back (CSFB) feature allows voice service over circuit switched infrastructure (3G or 2G).                                                                                              |

|                                                             | Firmware module update over AT command interfaces.  The feature can be enabled and configured through the +UFWUPD AT command.                                                                                                                                                                                                  |

| Firmware update Over<br>The Air (FOTA)                      | Embedded FOTA client to enable the Firmware module update over the cellular air interface.  The feature can be enabled and configured through the +UFWINSTALL AT command.                                                                                                                                                      |

<sup>&</sup>lt;sup>12</sup> Not supported by LARA-R204-02B, LARA-R220-62B, LARA-R280-02B and LARA-R281-02B modules product version.

<sup>&</sup>lt;sup>13</sup> Not supported by LARA-R203-02B, LARA-R203-03B, LARA-R204-02B, and LARA-R220-62B modules product version.

| Feature                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTE / 3G Rx Diversity                        | Improved cellular link quality and reliability on all operating bands, by means of 2 receiving antenna inputs.                                                                                                                                                                                                                                                                                                                                                              |

| GNSS via modem <sup>14</sup>                 | Full access to u-blox positioning chips and modules is available through a dedicated DDC (I2C) interface. This means that from any host processor, a single serial port can control the cellular module and the u-blox M8 positioning chip or module. For more details, see the GNSS implementation application note [4].                                                                                                                                                   |

| Embedded AssistNow<br>Software <sup>14</sup> | Embedded AssistNow Online and AssistNow Offline clients are available to provide better GNSS performance and faster Time-to-First-Fix. An AT command can enable / disable the clients.                                                                                                                                                                                                                                                                                      |

| CellLocate <sup>®14</sup>                    | Enables the estimation of device position based on the parameters of the mobile network cells visible to the specific device based on the CellLocate® database:                                                                                                                                                                                                                                                                                                             |

|                                              | <ul> <li>Normal scan: only the parameters of the visible home network cells are sent</li> <li>CellLocate® is available via a set of AT commands for CellLocate® service configuration and position request.</li> </ul>                                                                                                                                                                                                                                                      |

| Hybrid Positioning <sup>14</sup>             | The current module position is provided by a u-blox positioning chip or module or the estimated position from CellLocate® depending on which method provides the best and fastest solution according to the user configuration. Hybrid positioning is available via a set of AT commands that allow the configuration and the position request.                                                                                                                             |

| Wi-Fi via modem <sup>15</sup>                | Full access to Wi-Fi modules is available through a dedicated SDIO interface. This means that from any host processor a single serial port can control the cellular module and the short range communication module.                                                                                                                                                                                                                                                        |

| DTMF decoder <sup>16</sup>                   | During a voice call, the Dual-Tone Multi-Frequency detector analyses the RX speech (coming from remote party). The detected DTMF symbols can be output via the related URC.  The feature can be enabled and configured through the +UDTMFCFG +UDTMFD AT command.                                                                                                                                                                                                            |

| In-Band Modem <sup>15</sup>                  | In-Band modem solution for eCall and ERA-GLONASS emergency call applications over cellular networks implemented according to the 3GPP TS 26.267 specification [10].  When activated, the in-vehicle eCall / ERA-GLONASS system (IVS) creates an emergency call carrying both voice and data (including vehicle position data) directly to the nearest Public Safety Answering Point (PSAP) to determine whether rescue services should be dispatched to the known position. |

| Smart Temperature<br>Supervisor              | <ul> <li>Constant monitoring of the module board temperature:</li> <li>Warning notification when the temperature approaches an upper or lower predefined threshold</li> <li>Shutdown notified and forced when the temperature value is outside the specified range (shutdown suspended in case of an emergency call in progress)</li> <li>This feature can be enabled and configured via the +USTS AT command.</li> </ul>                                                   |

| Power saving                                 | The sensor measures the board temperature, which can differ from ambient temperature.  The power saving configuration is disabled by default, but it can be enabled and configured using the                                                                                                                                                                                                                                                                                |

| rower saving                                 | +UPSV AT command. When the power saving is enabled, the module automatically enters the low power idle-mode whenever possible, reducing current consumption.                                                                                                                                                                                                                                                                                                                |

|                                              | During idle-mode, the module processor core runs with the RTC 32 kHz reference clock, which is generated by the internal 32 kHz oscillator.                                                                                                                                                                                                                                                                                                                                 |

| Fast Dormancy                                | The Fast Dormancy feature, defined in 3GPP Rel.8, allows reduction of current consumption and network utilization during periods of data inactivity. It can be activated and configured by +UFDAC and +UDCONF=61 AT commands.                                                                                                                                                                                                                                               |

| LTE cDRX                                     | Both the Long DRX Cycle and the Short DRX cycle are supported for LTE Connected Discontinuous Reception, allowing reduction of current consumption and LTE network utilization during periods of data inactivity.                                                                                                                                                                                                                                                           |

| ODIS <sup>17</sup>                           | OMA-DM IMEI Sync (ODIS) is an AT&T functionality required at the cellular module level and used to identify the end device operating inside the network.                                                                                                                                                                                                                                                                                                                    |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Table 3: Some of the main features supported by LARA-R2 series modules

u-blox is extremely mindful of user privacy. When a position is sent to the CellLocate® server, u-blox is unable to track the SIM used or the specific device.

$<sup>^{14}</sup>$  Not supported by LARA-R204-02B, LARA-R211-02B-00 product versions.

<sup>&</sup>lt;sup>15</sup> Not supported by "02B", "62B", "82B", and "03B" product versions.

<sup>&</sup>lt;sup>16</sup> Not supported by LARA-R202-82B, LARA-R204-02B, and LARA-R220-62B modules product version.

<sup>&</sup>lt;sup>17</sup> Not supported by "03B" product version and LARA-R203-02B-34

## 2 Interfaces

## 2.1 Power management

## 2.1.1 Module supply input (VCC)

LARA-R2 series modules must be supplied through the three **VCC** pins by a DC power supply. Voltage must be stable, because during operation the current drawn from **VCC** can vary by some order of magnitude, especially due to the surging consumption profile of the GSM system (described in the LARA-R2 series system integration manual [2]). It is important that the system power supply circuit is able to support peak power.

LARA-R211 modules provide separate supply inputs over the three VCC pins:

- VCC pins #52 and #53 represent the supply input for the internal RF power amplifier, demanding

most of the total current drawn of the module when RF transmission is enabled during a

voice/data call

- VCC pin #51 represents the supply input for the internal baseband Power Management Unit and the internal transceiver, demanding a minor part of the total current drawn of the module when RF transmission is enabled during a voice/data call

## 2.1.2 RTC supply input / output (V\_BCKP)

When **VCC** voltage is within the valid operating range, the internal Power Management Unit (PMU) supplies the Real Time Clock (RTC) and the same supply voltage is available on the **V\_BCKP** pin. If the **VCC** voltage is under the minimum operating limit (e.g. during not powered mode), the **V\_BCKP** pin can externally supply the RTC.

## 2.1.3 Generic digital interfaces supply output (V\_INT)

LARA-R2 series modules provide a 1.8 V supply rail output on the **V\_INT** pin, which is internally generated when the module is switched on. The same voltage domain is used internally to supply the generic digital interfaces of the modules. The **V\_INT** supply output can be used in place of an external discrete regulator.

## 2.2 Antenna interfaces

### 2.2.1 Antenna RF interfaces

The modules have two RF pins with a characteristic impedance of 50  $\Omega$ . The primary antenna pin (ANT1) supports both Tx and Rx, providing the main antenna interface, while the secondary antenna pin (ANT2) supports Rx only for the LTE / 3G Rx diversity configuration.

### 2.2.2 Antenna detection

The **ANT\_DET** pin is an Analog to Digital Converter (ADC) input with a current source provided by LARA-R2 modules to sense the antenna(s) presence (as an optional feature). It evaluates the resistance from **ANT1** and **ANT2** pins to GND by means of an external antenna detection circuit implemented on the application board. For more details, see the LARA-R2 series system integration manual [2] and the u-blox AT commands manual [1].

## 2.3 System functions

## 2.3.1 Module power-on

LARA-R2 series modules can be switched on in one of the following ways:

Rising edge on the VCC input to a valid voltage for module supply, i.e. applying module supply: the

modules switch on if the VCC supply is applied, starting from a voltage value of less than 2.1 V,

with a rise time from 2.3 V to 2.8 V of less than 4 ms, reaching a proper nominal voltage value

within VCC operating range.

Alternately, for example if the fast rise time on **VCC** rising edge cannot be guaranteed by the application, the LARA-R2 series module can be switched on from not-powered mode as follows:

- RESET\_N input pin is held low by the external application during the VCC rising edge, so that the

module will switch on when the external application releases the RESET\_N input pin from the low

logic level, after the VCC supply voltage stabilizes at its proper nominal value within the operating

range

- PWR\_ON input pin is held low by the external application during the VCC rising edge, so that the

module will switch on when the external application releases the PWR\_ON input pin from the low

logic level, after the VCC supply voltage stabilizes at its proper nominal value within the operating

range

When the LARA-R2 series modules are in the power-off mode (i.e. properly switched off as described in section 2.3.2, with valid **VCC** module supply applied), they can be switched on as following:

- Low pulse on the PWR\_ON pin, which is normally set high by an internal pull-up, for a valid time

period (see section 4.2.8). The PWR\_ON line should be driven by open drain, open collector or

contact switch.

- Rising edge on the **RESET\_N** pin, i.e. releasing the pin from the low level, normally set high by an internal pull-up. The **RESET\_N** line should be driven by open drain, open collector or contact switch.

- RTC alarm, i.e. pre-programmed scheduled time by +CALA AT command.

### 2.3.2 Module power-off

LARA-R2 series can be properly switched off, saving current parameter settings in the module's non-volatile memory and performing a proper network detach, by:

- AT+CPWROFF command (see the u-blox AT commands manual [1]).

- Low pulse on the PWR\_ON pin, which is normally set high by an internal pull-up, for a valid time

period (see section 4.2.8). The PWR\_ON line should be driven by open drain, open collector or

contact switch.

An abrupt under-voltage shutdown occurs on LARA-R2 series modules when the **VCC** supply is removed. If this occurs, it is not possible to store the current parameter settings in the module's non-volatile memory or to perform the proper network detach.

An abrupt shutdown occurs on LARA-R2 series modules when a low level is applied on the **RESET\_N** pin, which is normally set high by an internal pull-up. If this occurs, it is not possible to store the current parameter settings in the module's non-volatile memory and to perform the proper network detach.

An over-temperature or an under-temperature shutdown occurs on LARA-R2 modules when the temperature measured within the cellular module reaches the dangerous area, if the optional Smart Temperature Supervisor feature is enabled and configured by the dedicated AT command. For more details, see the LARA-R2 series system integration manual [2] and the u-blox AT commands manual [1], +USTS AT command.

### 2.3.3 Module reset

LARA-R2 series modules can be reset (rebooted) by:

AT+CFUN command (see the u-blox AT commands manual [1]). This causes an "internal" or "software" reset of the module. The current parameter settings are saved in the module's non-volatile memory and a proper network detach is performed.

An abrupt "external" or "hardware" reset occurs when a low level is applied to the **RESET\_N** pin, which is normally set high by an internal pull-up, for a valid time period (see the section 4.2.9). This causes an "external" or "hardware" reset of the entire module, including the integrated power management unit, except for the RTC internal block: the **V\_INT** generic digital interfaces supply is switched off and all the digital pins are tri-stated, but the **V\_BCKP** supply and the RTC block are enabled. The current parameter settings are not saved in the module's non-volatile memory and a proper network detach is not performed. The **RESET\_N** line should be driven by open drain, open collector or contact switch.

## 2.3.4 Module / host configuration selection

The functionality of the **HOST\_SELECT** pin is not supported by any current product versions.

The modules include one pin (HOST\_SELECT) to select the module / host application processor configuration: the pin is available to select, enable, connect, disconnect and subsequently reconnect the HSIC interface.

### 2.4 SIM

### 2.4.1 SIM interface

A SIM card interface is provided on the **VSIM**, **SIM\_IO**, **SIM\_CLK**, **SIM\_RST** pins: the high-speed SIM/ME interface is implemented as well as the automatic detection of the required SIM supporting voltage.

Both 1.8 V and 3 V SIM types are supported (1.8 V and 3 V ME). Activation and deactivation with automatic voltage switch from 1.8 V to 3 V is implemented, according to ISO-IEC 7816-3 specifications. The SIM driver supports the PPS procedure for baud-rate selection, according to the values proposed by the SIM card/chip.

### 2.4.2 SIM detection

LARA-R2 series modules provide the SIM detection function over the **GPIO5** pin to sense the SIM card physical presence (as an optional feature) when the pin of the module is properly connected to the mechanical switch of the SIM car holder. For more details, see the LARA-R2 series system integration manual [2].

## 2.5 Serial communication

LARA-R2 series modules provide the following serial communication interfaces:

- Main UART interface: serial interface available for the communication with a host application processor (AT commands, data, FW update by means of FOAT), for FW update by means of the u-blox EasyFlash tool and for diagnostic.

- Auxiliary UART interface: serial interface available for AT commands communication with a host application processor, and for diagnostic.

- USB interface: Universal Serial Bus 2.0 compliant interface available for the communication with a host application processor (AT commands, data communication, FW update by means of the FOAT feature), for FW update by means of the u-blox EasyFlash tool and for diagnostic.

- HSIC interface: High-Speed Inter-Chip USB compliant interface available for the communication with a host application processor (AT commands, data communication, FW update by means of the FOAT feature), for FW update by means of the u-blox EasyFlash tool and for diagnostic.

- DDC interface: I2C bus compatible interface available for the communication with u-blox GNSS positioning chips/modules and with external I2C devices as an audio codec.

- SDIO interface: Secure Digital Input Output interface available for the communication with compatible u-blox short range radio communication Wi-Fi modules.

### 2.5.1 Main UART interface

LARA-R2 series modules include a 9-wire unbalanced main primary Universal Asynchronous Receiver/ Transmitter serial interface (UART) for communication with an external application host processor (AT commands, data communication, FW update by means of the FOAT feature), for FW update by means of the u-blox EasyFlash tool and for diagnostic.

### **UART** features are:

- Complete serial port with RS-232 functionality conforming to ITU-T V.24 recommendation [14], with CMOS compatible levels (0 V for low data bit / ON state, 1.8 V for high data bit / OFF state)

- Data lines (RXD output, TXD input), hardware flow control lines (CTS output, RTS input), modem status and control lines (DTR input, DSR output, DCD output, RI output) are provided

- Hardware flow control (default value), software flow control, or none flow control are supported

- Power saving indication available on the hardware flow control output (CTS line): the line is driven to the OFF state when the module is not prepared to accept data by the UART interface

- Power saving control over the RTS input or the DSR input can be enabled via AT+UPSV command (see the u-blox AT commands manual [1] and LARA-R2 series system integration manual [2])

- The following baud rates are supported: 9'600, 19'200, 38'400, 57'600, 115'200 (default baud rate

when autobauding is disabled), 230'400, 460'800, 921'600, 3'000'000, 3'250'000, 6'000'000 and

6'500'000 bit/s

- One-shot autobauding is supported and it is enabled by default: automatic baud rate detection is performed only once, at module start up. After the detection, the module works at the fixed baud rate (the detected one) and the baud rate can only be changed via AT command (see the u-blox AT commands manual [1], +IPR).

- The following frame formats are supported: 8N2, 8N1 (default format when automatic frame recognition is disabled), 8E1, 8O1, 7E1 and 7O1.

- One-shot automatic frame recognition is supported and it is enabled by default in conjunction with automatic baud rate detection (autobauding): the detection is performed only once, at module start up. After the detection, the module works at the detected frame format and it can only be changed via AT command (see u-blox AT commands manual [1], +ICF).

The main primary UART serial interface can be conveniently configured through AT commands: see the u-blox AT commands manual [1] (+IPR, +ICF, +IFC, &K,  $\Q$ , +UPSV, +USIO AT commands) and LARA-R2 series system integration manual [2].

## 2.5.1.1 Multiplexer protocol

LARA-R2 series modules include multiplexer functionality as per 3GPP TS 27.010 [9] on the main primary UART physical link. This is a data link protocol which uses HDLC-like framing and operates between the module (DCE) and the application processor (DTE), allowing a number of simultaneous sessions over the physical link (main primary UART): the user can concurrently use AT interface on one MUX channel and data communication on another MUX channel.

The following virtual channels are available (see the Mux implementation application note [5]):

- Channel 0: Multiplexer control

- Channel 1 5: AT commands / data connection

- Channel 6: GNSS data tunneling

## 2.5.2 Auxiliary UART interface

The auxiliary UART interface is not supported by the "02B", "62B" and "82B" product versions of the LARA-R202, LARA-R203, LARA-R204, LARA-R220, LARA-R280, and LARA-R281 modules, and by the "02B-00", "02B-01" and "02B-02" product versions of LARA-R211 modules.

LARA-R2 series modules include a 3-wire unbalanced auxiliary secondary Universal Asynchronous Receiver/Transmitter serial interface (AUX UART) for AT commands communication with an external application host processor, and for diagnostic (CSD or PSD are not supported).

The auxiliary secondary UART interface is disabled by default, and it can be enabled by dedicated AT command (see the u-blox AT commands manual [1], +USIO) as alternative function of the DDC (I2C) interface' pins, in mutually exclusive way with the DDC (I2C) interface.

### AUX UART features are:

- 3-wire serial port with RS-232 functionality conforming to ITU-T V.24 recommendation [14], with CMOS compatible signal levels (0 V for low data bit / ON state, 1.8 V for high data bit / OFF state)

- Data lines (SCL pin as AUX UART data output, SDA pin as AUX UART data input)

- Software flow control, or none flow control (default value) are supported

- The following baud rates are supported: 9'600, 19'200, 38'400, 57'600, 115'200 (default baud rate

when autobauding is disabled), 230'400, 460'800, 921'600, 3'000'000, 3'250'000, 6'000'000 and

6'500'000 bit/s

- One-shot autobauding is supported and it is enabled by default: automatic baud rate detection is

performed only once, at module start up. After the detection, the module works at the fixed baud

rate (the detected one) and the baud rate can only be changed via AT command (see the u-blox AT

commands manual [1], +IPR).

- The following frame formats are supported: 8N2, 8N1 (default format when automatic frame recognition is disabled), 8E1, 8O1, 7E1 and 7O1.

- One-shot automatic frame recognition is supported and it is enabled by default in conjunction with automatic baud rate detection (autobauding): the detection is performed only once, at module start up. After the detection, the module works at the detected frame format and it can only be changed via AT command (see u-blox AT commands manual [1], +ICF).

- The Data Terminal Ready physical line is not available, but the logical Data Terminal Ready line is always to ON state

The multiplexer protocol is not supported over the auxiliary secondary UART physical link.

The auxiliary secondary UART serial interface can be conveniently configured through AT commands: see the u-blox AT commands manual [1] (+IPR, +ICF, +IFC, &K, \Q, +UPSV, +USIO AT commands) and LARA-R2 series system integration manual [2].

### 2.5.3 USB interface

LARA-R2 series modules include a USB High-Speed 2.0 compliant interface with a maximum 480 Mbit/s data rate according to the Universal Serial Bus specification revision 2.0 [15]. The module itself acts as a USB device and can be connected to any compatible USB host.

The USB interface is available for communication with a host application processor (AT commands, data communication, FW update by means of the FOAT feature), for FW update by means of the u-blox EasyFlash tool and for diagnostics.

The **USB\_D+** / **USB\_D-** lines carry the USB data and signaling. The USB interface is automatically enabled by an external valid USB VBUS supply voltage (5.0 V typical) applied on the **VUSB\_DET** pin.

The USB interface of LARA-R2 series modules makes several USB functions available with various capabilities and purposes, such as:

- CDC-ACM for AT commands and data communication

- CDC-ACM for GNSS tunneling

- CDC-ACM for SAP (SIM Access Profile)

- CDC-ACM for Diagnostic log

- CDC-NCM for Ethernet-over-USB

- CDC-ACM for GNSS tunneling is not supported by the LARA-R204-02B and LARA-R211-02B-00 product versions.

- CDC-ACM for SAP and CDC-NCM for Ethernet-over-USB are not supported by any current product versions.

The USB interface provides the following set of USB functions:

- 6 CDC-ACM modem COM ports enumerated as follows:

- o USB1: AT and data

- o USB2: AT and data

- o USB3: AT and data

- USB4: GNSS tunneling

- USB5: SAP (SIM Access Profile)

- USB6: diagnostic log

The user can concurrently use the AT command interface on one CDC, and Packet-Switched / Circuit-Switched Data communication on another CDC.

For more details regarding USB capabilities, see the LARA-R2 series system integration manual [2].

USB drivers are available for the following Windows and Windows Embedded operating system platforms:

- Windows 7

- Windows 8

- Windows 8.1

- Windows 10

- Windows Embedded CE 6.0

- Windows Embedded Compact 7

- Windows Embedded Compact 2013

- Windows 10 IoT

LARA-R2 series modules are compatible with the standard Linux/Android USB kernel drivers.

#### HSIC interface 2.5.4

The HSIC interface is not supported by current product versions, except for diagnostic purposes.

LARA-R2 series modules include a USB High-Speed Inter-Chip compliant interface with a maximum 480 Mbit/s data rate as per the High-Speed Inter-Chip USB Electrical Specification Version 1.0 [16] and USB specification revision 2.0 [15]. The module itself acts as a device and can be connected to any compatible host.

The HSIC interface is available for communication with a host application processor (AT commands, data communication, FW update by means of the FOAT feature), for FW update by means of the u-blox EasyFlash tool and for diagnostics.

The HSIC interface consists of a bi-directional DDR data line (HSIC DATA) for transmitting and receiving data synchronously with the bi-directional strobe line (HSIC\_STRB).

The modules also include the HOST\_SELECT pin to select the module / host application processor configuration: the pin is available to select, enable, connect, disconnect and subsequently reconnect the HSIC interface.

#### 2.5.5 DDC (I2C) interface

Dedicated AT commands for the communication with u-blox GNSS receivers over DDC (I2C) are not supported by LARA-R204-02B and LARA-R211-02B-00 product versions.

LARA-R2 series modules include an I2C-bus compatible DDC interface (SDA, SCL)<sup>18</sup> available to communicate with a u-blox GNSS receiver and with external I2C devices as an audio codec: LARA-R2 module acts as an I2C host which can communicate with I2C local devices in accordance with the I2C bus specifications [17].

For more details regarding DDC (I2C) interface usage and the integration with a u-blox GNSS receiver, see the LARA-R2 series system integration manual [2], GNSS implementation application note [4], and the I2C and GNSS AT commands description in the u-blox AT commands manual [1].

#### **SDIO** interface 2.5.6

The SDIO interface is not supported by "02B", "62B", "82B", and "03B" product versions.

LARA-R2 series modules include a 4-bit Secure Digital Input Output interface (SDIO\_D0, SDIO\_D1, SDIO\_D2, SDIO\_D3, SDIO\_CLK, SDIO\_CMD) designed to communicate with external compatible u-blox short range radio communication Wi-Fi modules.

### 2.6 Audio

Audio is not supported by LARA-R204-02B, LARA-R220-62B product versions.

LARA-R2 series modules support Voice over LTE (VoLTE) as well as Circuit-Switched Fall-Back (CSFB) from LTE to 3G or 2G radio bearer for providing audio services.

LARA-R2 series modules include a 4-wire I2S digital audio interface (I2S TXD, I2S RXD, I2S CLK, I2S WA) that can be configured by AT command in PCM mode (short synchronization signal) or in normal I2S mode (long synchronization signal) to transfer digital audio data to/from an external device as an audio codec.

UBX-16005783 - R28 Interfaces Page 18 of 48

<sup>&</sup>lt;sup>18</sup> SDA and SCL pins can be alternatively configured, in a mutually exclusive way, as auxiliary UART interface (AUX UART) on LARA-R2 series modules, except the "02B", "62B" and "82B" versions of the LARA-R202, LARA-R203, LARA-R204, LARA-R220, LARA-R280 and LARA-R281 modules, and the "02B-00", "02B-01" and "02B-02" versions of LARA-R211 modules.

For more details regarding internal audio processing system capabilities, I2S digital audio interface possible configurations, usage and guideline for the integration with an external digital audio device as an audio codec, see the LARA-R2 series system integration manual [2] and the audio sections in the u-blox AT commands manual [1].

## 2.7 Clock output

LARA-R2 series modules provide digital clock output functionality on the **GPIO6** pin, which can be configured to provide a 13 MHz or 26 MHz square wave. This is mainly designed to feed the clock input of an external audio codec, as the clock output can be configured in "Audio dependent" mode (generating the square wave only when the audio path is active), or in "Continuous" mode.

For more details, see the u-blox AT commands manual [1], +UMCLK AT command.

### **2.8 GPIO**

LARA-R2 series modules include 9 pins (**GPIO1-GPIO5**, **I2S\_TXD**, **I2S\_RXD**, **I2S\_CLK**, **I2S\_WA**) that can be configured as general purpose input/output or to provide custom functions as summarized in the Table 4 (for further details, see the LARA-R2 series system integration manual [2] and the GPIO section in the u-blox AT commands manual [1]).

| Function                          | Description                                                                                        | Default GPIO                         | Configurable GPIOs                   |

|-----------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------|

| Network status indication         | Network status: registered home network, registered roaming, data transmission, no service         |                                      | GPIO1-GPIO4                          |

| GNSS supply enable <sup>19</sup>  | Enable/disable the supply of u-blox GNSS receiver connected to the cellular module                 | GPIO2                                | GPIO1-GPIO4                          |

| GNSS data ready <sup>19</sup>     | Sense when u-blox GNSS receiver connected to the module is ready for sending data by the DDC (I2C) | GPIO3                                | GPIO3                                |

| GNSS RTC sharing <sup>20</sup>    | RTC synchronization signal to the u-blox GNSS receiver connected to the cellular module            |                                      | GPIO4                                |

| SIM card detection                | External SIM card physical presence detection                                                      | GPIO5                                | GPIO5                                |

| SIM card hot<br>insertion/removal | Enable / disable SIM interface upon detection of external SIM card physical insertion / removal    |                                      | GPIO5                                |

| I2S digital audio<br>interface    | I2S digital audio interface                                                                        | 12S_RXD, 12S_TXD,<br>12S_CLK, 12S_WA | 12S_RXD, 12S_TXD,<br>12S_CLK, 12S_WA |

| Wi-Fi control <sup>20</sup>       | Control of an external Wi-Fi chip or module                                                        |                                      |                                      |

| General purpose input             | Input to sense high or low digital level                                                           |                                      | All                                  |

| General purpose output            | Output to set the high or the low digital level                                                    | GPIO4                                | All                                  |

| Pin disabled                      | Tri-state with an internal active pull-down enabled                                                | GPIO1                                | All                                  |

Table 4: GPIO custom functions configuration

<sup>&</sup>lt;sup>19</sup> Not supported by LARA-R204-02B and LARA-R211-02B-00 product versions: GPIO2 and GPIO3 pins are by default disabled

$<sup>^{\</sup>rm 20}$  Not supported by "02B", "62B", "82B", and "03B" product versions

## Pin definition

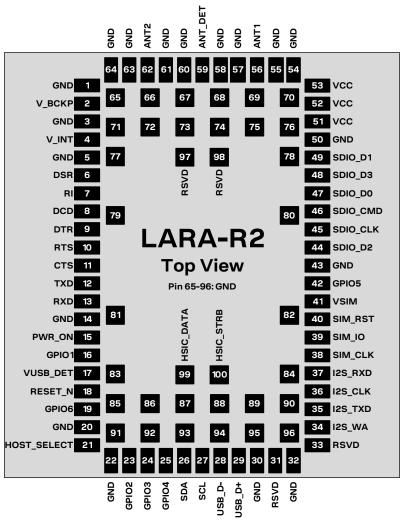

### Pin assignment 3.1

Figure 2: LARA-R2 series pin assignment (top view)

| No | Name   | Power<br>domain | I/O | Description                              | Remarks                                                                                                                                                                     |

|----|--------|-----------------|-----|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | GND    | -               | N/A | Ground                                   | All the GND pins must be connected to ground                                                                                                                                |

| 2  | V_BCKP | -               | I/O | Real Time Clock supply input/output      | V_BCKP = 1.8 V (typical) generated by the module to supply<br>the RTC when VCC voltage is within valid operating range.<br>See section 4.2.2 for detailed electrical specs. |

| 3  | GND    | -               | N/A | Ground                                   | All the GND pins must be connected to ground                                                                                                                                |

| 4  | V_INT  | -               | 0   | Generic Digital Interfaces supply output | V_INT = 1.8 V (typical) generated by the module when it is switched-on and with the RESET_N pin is not forced low. See section 4.2.2 for detailed electrical specs.         |

| 5  | GND    | -               | N/A | Ground                                   | All the GND pins must be connected to ground                                                                                                                                |

| 6  | DSR    | GDI             | 0   | UART data set ready                      | Circuit 107 (DSR) in ITU-T V.24. Output driver class A. PU/PD class a. Value at internal reset: T/PU. See section 4.2.14 for detailed electrical specs.                     |

| No | Name        | Power<br>domain | I/O | Description                                        | Remarks                                                                                                                                                                                 |

|----|-------------|-----------------|-----|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7  | RI          | GDI             | 0   | UART ring indicator                                | Circuit 125 (RI) in ITU-T V.24.  Output driver class A. PU/PD class a.  Value at internal reset: T/PD.  See section 4.2.14 for detailed electrical specs.                               |

| 8  | DCD         | GDI             | 0   | UART data carrier detect                           | Circuit 109 (DCD) in ITU-T V.24. Output driver class A. PU/PD class a. Value at internal reset: T/PD. See section 4.2.14 for detailed electrical specs.                                 |

| 9  | DTR         | GDI             | I   | UART data terminal ready                           | Circuit 108/2 (DTR) in ITU-T V. 24. Internal active pull-up to V_INT enabled. PU/PD class a. Value at internal reset: T/PU. See section 4.2.14 for detailed electrical specs.           |

| 10 | RTS         | GDI             | I   | UART ready to send                                 | Circuit 105 (RTS) in ITU-T V.24. Internal active pull-up to V_INT enabled. PU/PD class a. Value at internal reset: T/PU. See section 4.2.14 for detailed electrical specs.              |

| 11 | CTS         | GDI             | 0   | UART clear to send                                 | Circuit 106 (CTS) in ITU-T V.24.  Output driver class A. PU/PD class a.  Value at internal reset: T/PU.  See section 4.2.14 for detailed electrical specs.                              |

| 12 | TXD         | GDI             | I   | UART data input                                    | Circuit 103 (TxD) in ITU-T V.24. Internal active pull-up to V_INT enabled. PU/PD class a. Value at internal reset: T/PD. See section 4.2.14 for detailed electrical specs.              |

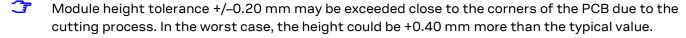

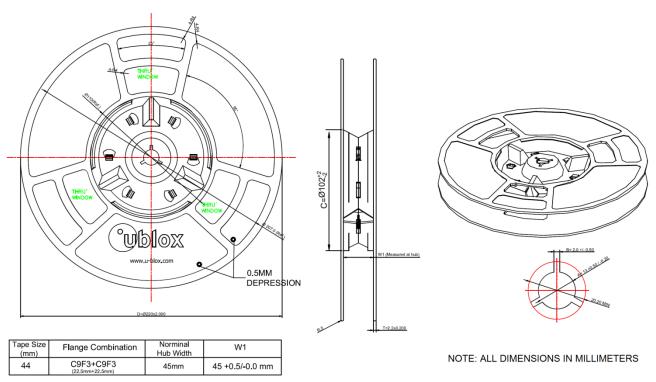

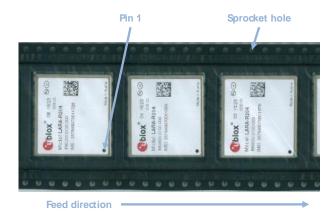

| 13 | RXD         | GDI             | 0   | UART data output                                   | Circuit 104 (RxD) in ITU-T V.24.  Output driver class A. PU/PD class a.  Value at internal reset: T/PU.  See section 4.2.14 for detailed electrical specs.                              |